Graphene Based Triple-Gate-Platforms for Novel Tunnel Field-Effect Transistors

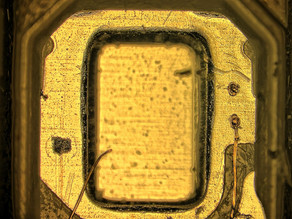

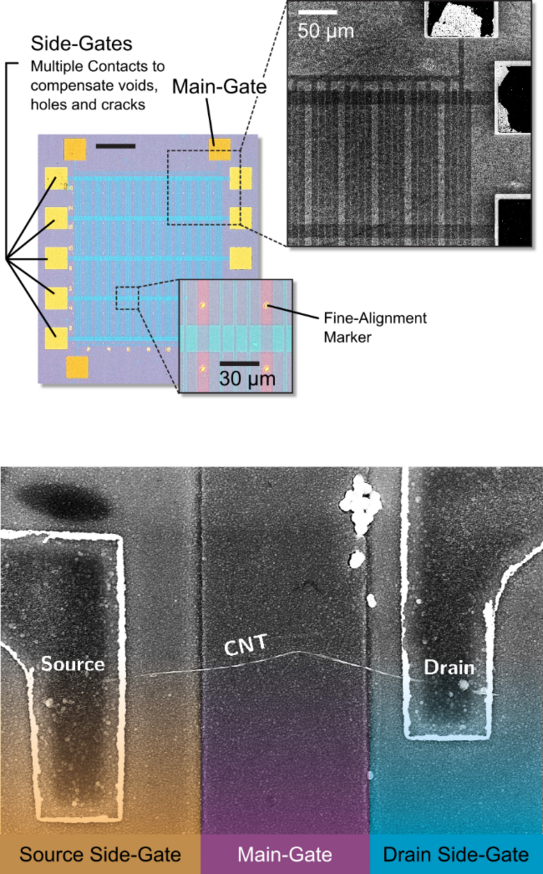

Compared to conventional field-effect transistors (FETs), tunnel-FETs (TFETs) allow for inverse sub-threshold slopes below 60 mV/decade at room temperature. Therefore, TFETs have the potential of ultra low-power consumption. Ideally, carrier transport in TFET devices only depends on band-to-band tunnelling and energy filtering in the Boltzmann regime. By applying individual potentials to buried gate electrodes in close proximity, different band configurations along a semiconductor channel region can be electrostatically adjusted to control the tunneling probability. However, to achieve a homogenous electric field distribution along the channel, fabrication of buried and mutually insolated electrodes (buried triple-gate, BTG) can be challenging for planar processes. In this project we propose a novel concept of a graphene-based BTG platform for TFET characterization. The advantage of this concept is that at least one gate-electrode is made of an almost atomically thin graphene layer, which enables fabrication of thin vertically stacked graphene/oxide-heterostructures. The proposed concept allows for sharp electrostatic doping profiles and very narrow band transitions. This in turn, increases the band-to-band tunnelling probability and provides very steep subthreshold slopes in TFET characterization.

We plan to integrate low-dimensional WS2 for fabrication of proof-of-concept TFETs. The devices will be analyzed by advanced characterization techniques, including a dedicated in operando method based on high resolution photoemission electron microscopy (PEEM). Other characterization techniques include 2D Raman Spectroscopy, in situ X-ray photoelectron spectroscopy (XPS), and electrical characterization in a temperature range between 8 K and 500 K. The proposed design is versatile and allows for integration of any semiconducting 1D- or 2D-material.

DFG Research Grants

- Titel: Graphene Based Triple-Gate-Platforms for Novel Tunnel Field-Effect Transistors

- Project Number: 524569125

- Project Duration: 01.10.2023 - 30.09.2026

- Funding: Individual Research Grant

Joint project with Dr. G. Zamborlini (Cinchetti Group, Physics Department)